Training

Practical Learning

Hands-on sessions focused on real-world chip design, from IP to verification. Develop skills that match the latest industry requirements.

Expert Guidance

Learn directly from industry professionals with proven VLSI experience.Get personalized mentorship to clarify concepts and challenges.

Project Exposure

Work on design projects to strengthen technical and problem-solving skills.Build a strong portfolio that adds value to your career.

Career Growth

Gain the skills and confidence to excel in the semiconductor industry.Open doors to global opportunities in chip design and verification.

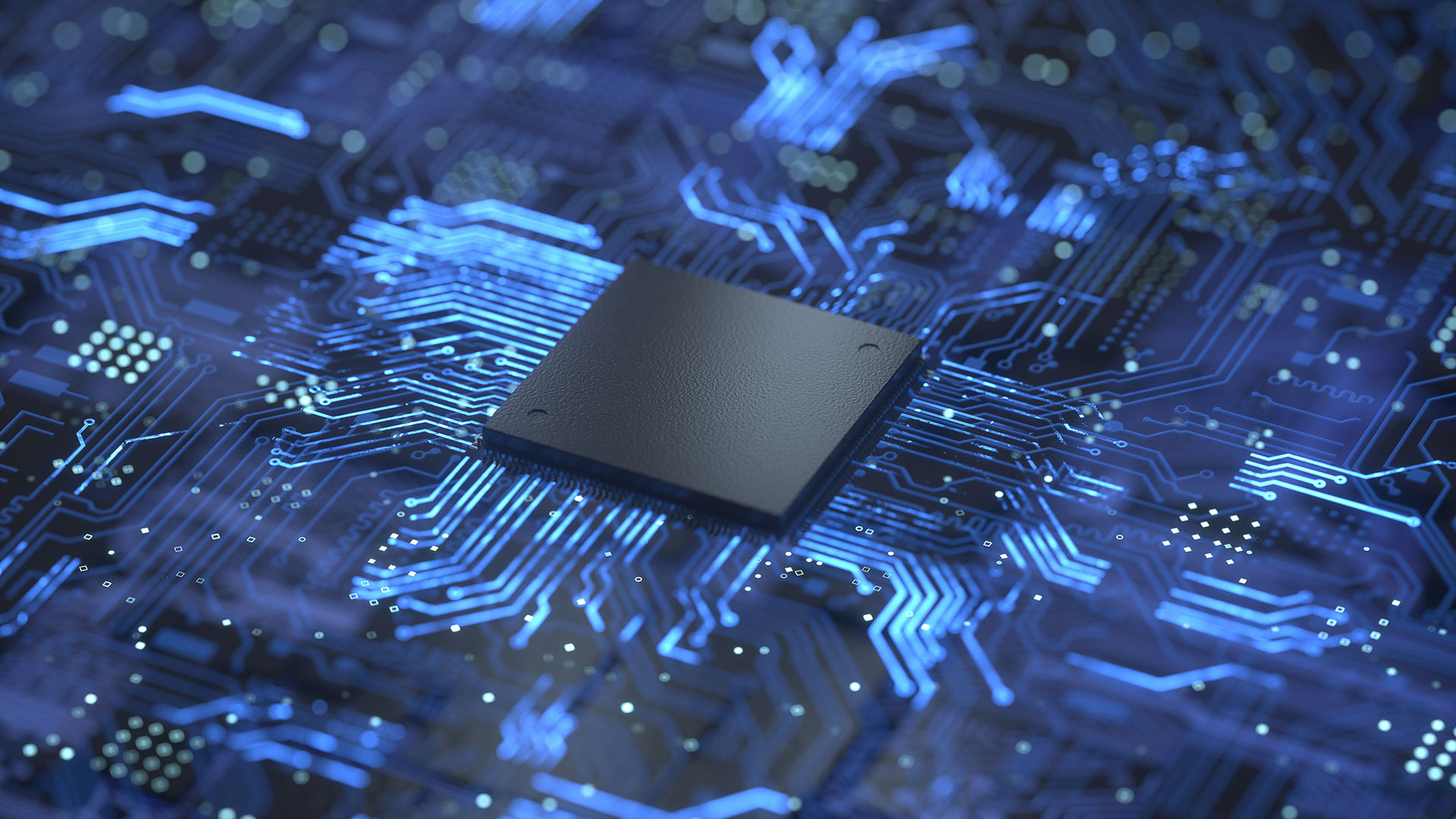

Circuit Design

The Circuit Design training provides in-depth knowledge of designing analog, digital, and mixed-signal circuits. Learners will explore the principles of circuit theory, transistor-level design, and advanced simulation techniques. Topics include biasing, logic gates, combinational/sequential circuits, amplifiers, and mixed-signal interface design. The training emphasizes practical exposure using industry-standard EDA tools, enabling participants to translate theoretical designs into optimized, functional circuits.

Key Learning Points:

- Mastering fundamentals of analog, digital, and mixed-signal circuit design.

- Applying simulation and analysis for real-world design validation.

- Learning optimization techniques for low-power and high-performance circuits.

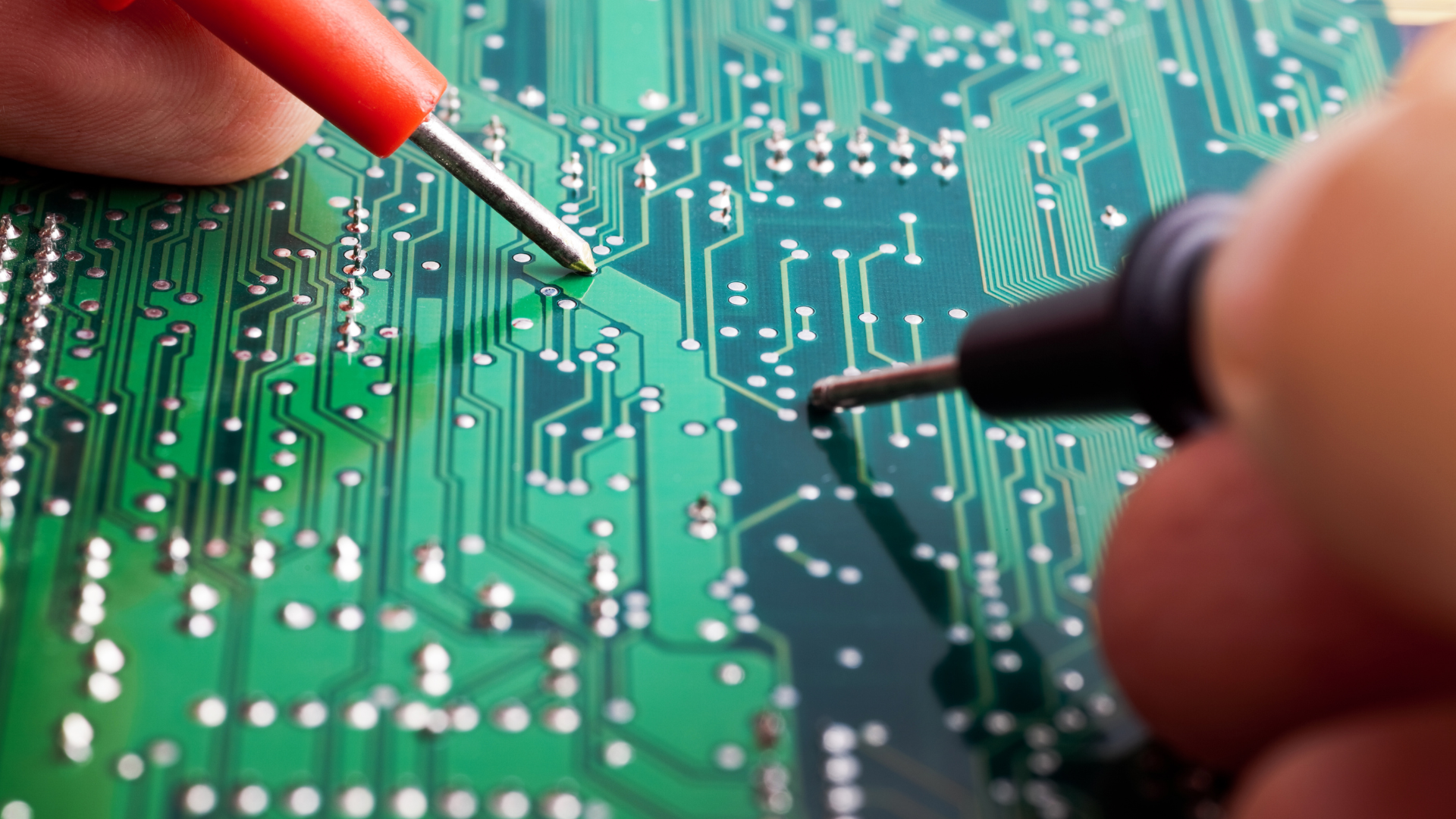

Analog Layout

Our Analog Layout training focuses on teaching layout design skills essential for analog and mixed-signal ICs. Students will understand the physical representation of circuits, including placement, routing, matching, symmetry, and parasitic handling. The training emphasizes best practices in analog layout, such as common-centroid techniques, shielding, and guard rings to achieve robust designs. Using industry tools, learners will gain hands-on practice in layout versus schematic (LVS), design rule check (DRC), and parasitic extraction.

Key Learning Points:

- Understanding layout fundamentals for analog/mixed-signal circuits.

- Gaining expertise in LVS, DRC, and parasitic extraction checks.

- Learning matching and symmetry techniques for precision design.

IP Design

Our IP Design training equips learners with the knowledge to create reusable Intellectual Property (IP) blocks that are essential in modern SoC (System-on-Chip) and ASIC design. Participants will gain an understanding of IP architecture, development flow, integration strategies, and verification methodologies. The training covers aspects like IP specification, RTL coding, functional simulation, verification, and IP packaging for reuse across multiple projects. Emphasis is placed on industry standards, scalability, and efficiency to ensure that students can build optimized, high-performance IP blocks.

Key Learning Points:

- Understanding IP architecture, specification, and development lifecycle.

- Gaining expertise in IP verification and validation methodologies.

- Learning techniques for IP reuse, integration, and scalability.

Physical Design

The Physical Design training covers the back-end design process in VLSI, taking a design from RTL to GDSII. Topics include synthesis, floorplanning, placement, clock tree synthesis (CTS), routing, timing closure, and design-for-manufacturability. Participants will gain an understanding of how physical constraints impact chip performance, power, and area. Practical sessions with industry-standard EDA tools will prepare learners to solve real-world challenges such as congestion, timing violations, and power optimization.

Key Learning Points:

- Mastering the complete RTL-to-GDSII physical design flow.

- Learning timing closure, congestion management, and power optimization.

- Gaining practical exposure to EDA tools used in industry.

Static Timing Analysis (STA)

Our STA training focuses on one of the most important aspects of VLSI design: ensuring timing correctness of digital circuits. Students will learn the principles of setup time, hold time, clock skew, and timing paths. The training covers constraint writing (SDC), analyzing timing reports, debugging violations, and applying fixes through techniques like buffering, resizing, and multi-corner analysis. By the end, participants will be able to perform comprehensive timing checks and ensure robust, high-speed chip designs.

Key Learning Points:

- Understanding timing concepts: setup, hold, skew, and slack.

- Writing constraints and analyzing STA reports for closure.

- Applying practical timing fixes and optimizations.

Design Verification

The Design Verification training prepares students to ensure that chip designs meet functional requirements before fabrication. The program covers simulation-based verification, testbench architecture, SystemVerilog/UVM methodologies, functional coverage, and assertion-based verification. Learners will explore verification planning, constrained-random testing, regression management, and debugging techniques. By applying these methods in hands-on labs, participants will develop the ability to find and fix design flaws efficiently, saving time and cost in the chip development cycle.

Key Learning Points:

- Understanding verification methodologies (SystemVerilog/UVM).

- Building testbenches and implementing functional coverage.

- Applying debugging and regression testing techniques.

.png)